CDC is an abbreviation of Clock Domain Crossing, which is one of the most critical issues in digital IC design when there are multiple asynchronous clock domains in the chips and signals are crossed from one clock domain to another.

What are CDC issues when crossing signals between asynchronous clock domains?

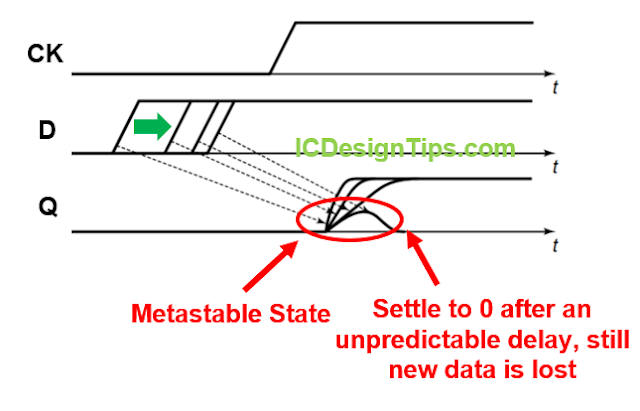

Synchronous clocks show constant phase relationships, whereas asynchronous clocks exhibit variable phase and time relationships. Thus, when a signal crosses between two asynchronous clock domains, there are likely setup or hold time violations at the destination flip-flop. This would cause metastability, hence resulting in metastability propagation and data loss in the destination clock domain as shown in the following waveform. To read more about setup time, hold time, and metastability, check here.

How do we avoid the CDC metastability issue?

The answer is NO. We cannot avoid metastability or timing violations when crossing between asynchronous clock domains since the crossing signal is asynchronous and its arrival time is unpredictable when captured by the destination flip-flop. Note that STA tools consider these timing paths (crossing between asynchronous clock domains) as false paths and there is no timing optimization during synthesis or place and route for these timing paths. Hence, timing violations are likely to happen, which leads to metastability.It is however possible to avoid the propagation of metastability to other parts of the chip and prevent data loss/coherency by using synchronizer circuits. Depending on the signal function, different types of synchronizers are required to avoid these CDC issues. Both Cadence and Synopsys have corresponding tools (JasperGold CDC and SpyGlass) to verify if the chip (RTL) has any CDC issues (missing synchronizers) so that it can be checked, waived, or fixed (by designers) as early as possible in the design cycle.

Various types of synchronizers required in digital IC design are to be discussed in the next articles.

Various types of synchronizers required in digital IC design are to be discussed in the next articles.

Recommended Articles for Understanding Metastability as well as Setup and Hold Time:

Comments

Post a Comment